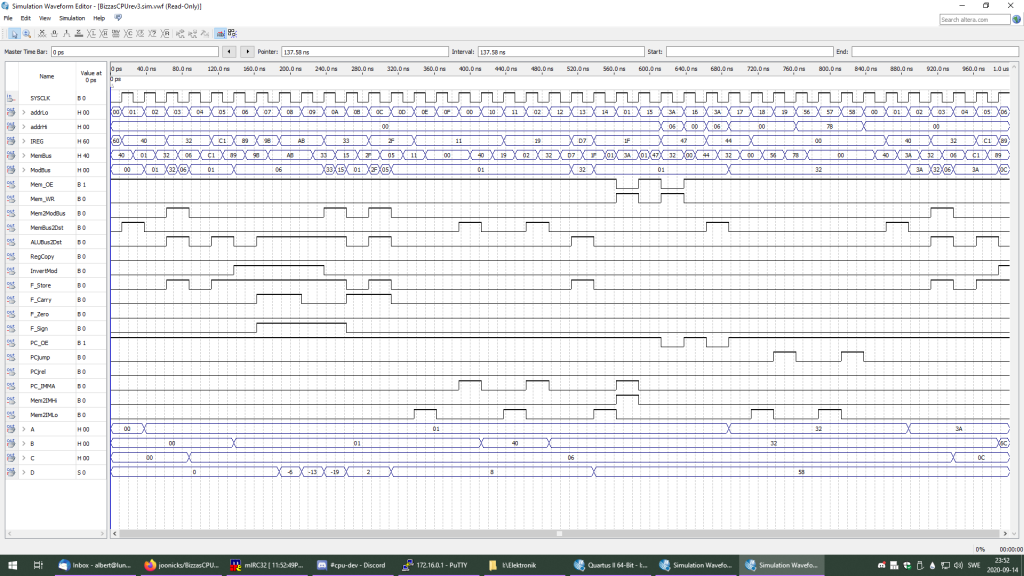

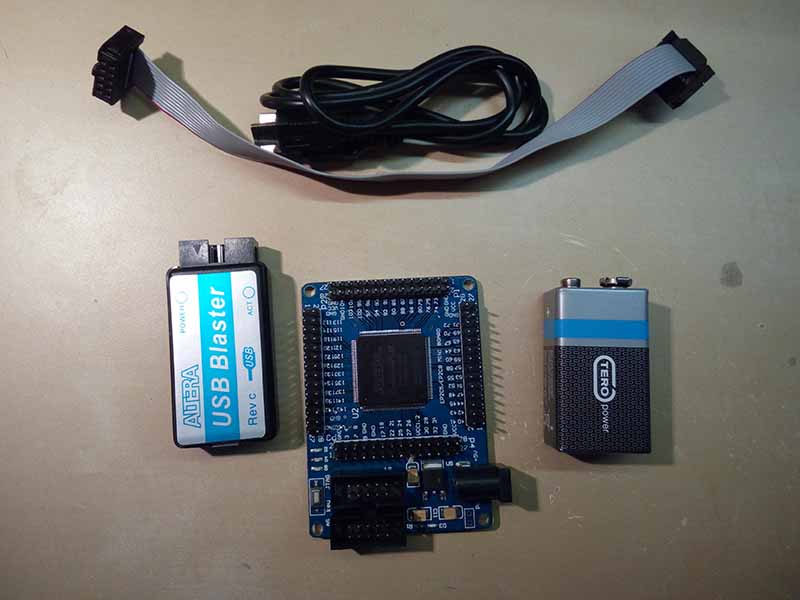

After two years of developing and simulating, BizzasCPU today took the step into actual hardware. The first ever upload into an actual FPGA started the parade of blinking LEDs and established that it works quite well. In fact the first run was so fast that it needed to be slowed down by a factor of 10,000 to be able to verify without a doubt that it is fully functional and operates as expected.

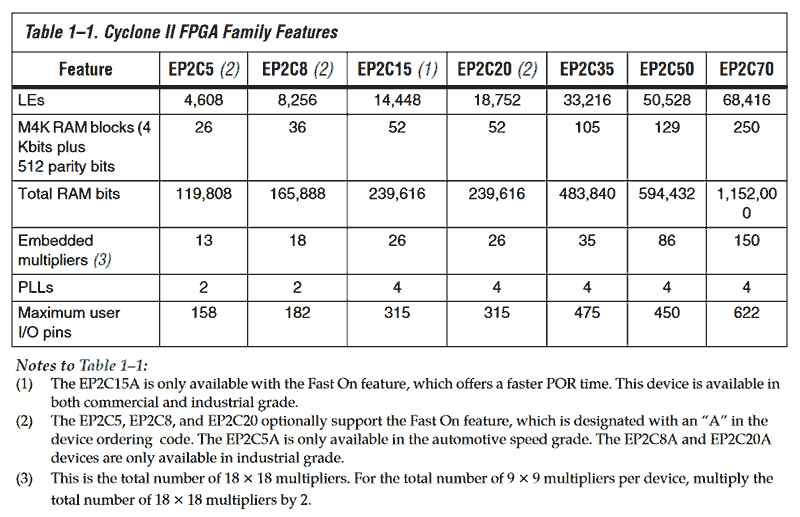

The host FPGA was a Terasic DE10-Nano development board and the operating frequency was 12.5MHz. The frequency however can most likely be bumped up significantly, if needed. The BizzasCPU design has much higher MIPS per Clock compared to a 6502 or Z80, but instruction complexity is somewhere inbetween, being more versatile than 6502, but less than a Z80.

Now follows the need for a proper assembler and more IO to make it more fun to play around with. Just 8 LEDs blinking is not the most inspiring.

Of course it will now be fun to run around bragging about my very own CPU design. Future will tell if anyone ever notices.